"…sequential computers are approaching a fundamental physical

limit on their potential power. Such a limit is the speed of light…"

![]()

|

|

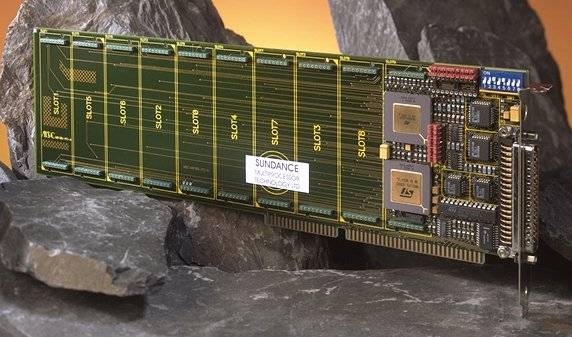

The interface to the PC provides a signal to transputer serial link and a system services port. This allows software running on the PC to reset, analyze, communicate with, and monitor the error flag of a transputer connected to or on the MSC008. Data can be transferred to and from the link interface using programmed I/O or DMA transfer mechanism allowing data transfer to go on without processor intervention. On some PCs this will result in a faster transfer rate than can be achieved using programmed I/O. Interrupts can be generated on link events, on error being asserted, or at the end of DMA transfer, freeing the processor from polling the MSC008 to detect these events.

The TRAM slots on the MSC008 are connected into a pipeline using two of the four links from each slot. The remaining two links from slots 1 to 9 and link 3 from slot 0 are connected to the IMSC004 link switch which allows these links to be soft-wired together to form transputer networks other than a pipeline. Control and configuration of the link switch is performed by an IMS T225 16 bit transputer.

|

This page is copyright ©1995, Sundance Multiprocessor Technology Ltd.