Welcome to Ram

Meenakshisundaram's Transputer Home Page

"…sequential computers are

approaching a fundamental physical

limit on their potential power. Such a limit is

the speed of light…"

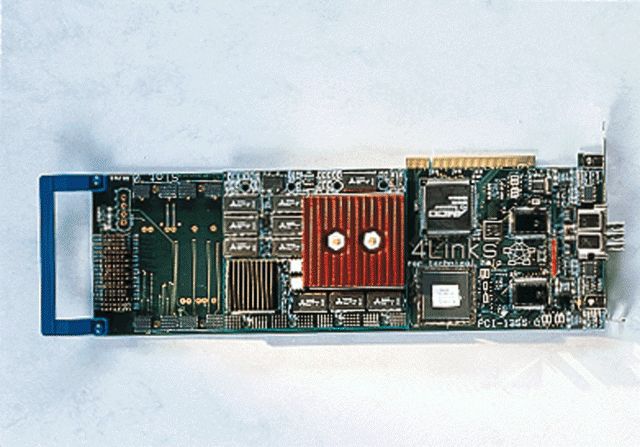

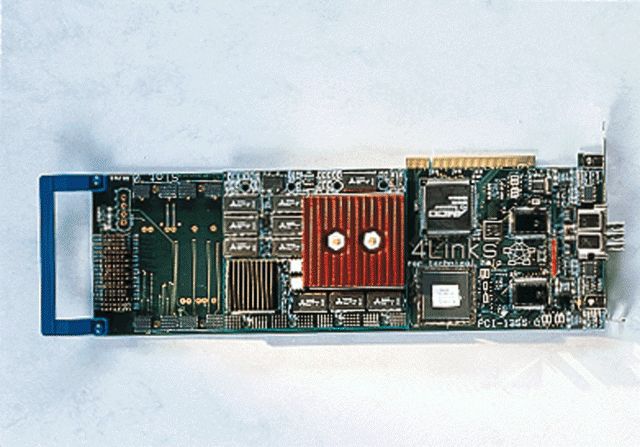

Alpha Data ADC-HPCI PCI bus interface

development board

for IEEE 1355 DS-DE links

- Links may be used point-to-point, or may be connected via hubs based on

routing switch chips such as the 32-port SGS-THOMSON C104.

- The PCI 32-bit access based interface is much faster than any older

technology (such as ISA)

- The programmer has full control of packets, with a clean address

mapping of the C101 registers.

- Packet payloads may be any multiple of 4 bytes. Examples include ATM

payloads at 48 bytes, MPEG2 at 192 bytes, or T9000 transputer at 32 bytes.

Packets of different sizes for different destinations may be interleaved on

the same link

- 1355's remote power option is included on both links, to power remote

devices from the board

- Development of 1355 systems

- IHDEN development (In-Home Digital Entertainment Network)

- PC clusters / Internet servers

- Video-on-Demand (VoD) servers

- Host interface for T9 systems

- HTRAM motherboard

- FIFO between two computers

- Virtual transputers, particularly with "Occam for All"

- Optional sockets for Size4 and Size2 HTRAM slots connect via jumpers to

provide a variety of configurations.

- An option provides a Reset connector for controlling an external T9000

system

- A further option is a socketed larger PLD, for enhanced performance

from future revisions of the PLD equations

BAR 0 Operation registers of S5933 PCI chip, reserved

BAR 1 64 words of 32

bits I/O space, C101 registers for Link 0

BAR 2 64 words of 32 bits I/O

space, C101 registers for Link 1

BAR 3 I/O space, writing generates hard

reset to both C101s

BAR 4 not used

BAR 5 not available

Software provided includes C routines for determining the base address

registers set up by the BIOS, and for transmitting and receiving virtual channel

packets.

EMC features on all boards include AT&T buffers with minimised

output skew, common mode chokes on outputs, use of Harlink bracket and EMC

gasket for 1355 connectors, and split 5V plane to minimise coupling to link

signals. A particular EMC feature is the use of a spread-spectrum link clock to

reduce emissions from the cables.

The ADC-HPCI provides a simple interface between the PCI bus and two 1355

links. The links are buffered in accordance with the DS-DE specification of IEEE

1355 (and also to be ISO/IEC 14575CD). 1355 links provide an exceptionally

light-weight Virtual Channel protocol for serial communication between

processors, between I/O systems, or between I/O systems and processors. The

standard PCI "large card" form-factor allows PCs, PowerPCs, or Alphas to use

1355 links.

| Processor |

DEC Alpha 21066 fully-pipelined 64-bit RISC architecture

- 233MHz (466 mips, 233MFLOPS) using dual instruction issue

- IEEE and VAX-compatible floating point

- High bandwidth 64-bit memory controller

- Memory management

- 8k on-chip data and instruction caches

- Secondary cache controller

- Asynchronous PCI I/O controller

- Intel compatible PCI bus

INMOS T9000

- Running at 25MHz

- Supporting Virtual Channel Routing (VCR)

- Includes 4 DS links based on the IEEE P1355 standard

|

| Memory |

DEC Alpha

- 8MB to 32MB of 70ns DRAM

- 256K to 1MB 15ns external cache SRAM

INMOS T9000

|

| Host interface |

Connected to an HTRAM carrier board |

| Software |

3L Parallel C/AXP compiler with parallel network support

- (including DEC GEM compiler).

- IPLib and fast maths libraries

INMOS T9000 toolset for the T9000

|

| Warranty |

12 months from date of invoice |

This page is copyright ©1999 Alpha

Data Parallel Systems Ltd

![]()